| |

|

| 阅读网 -> 明星艺术 -> 硬件工程师设计出错是什么体验? -> 正文阅读 |

|

|

[明星艺术]硬件工程师设计出错是什么体验? |

| [收藏本文] 【下载本文】 |

|

硬件工程师设计出错是什么体验? 关注问题?写回答 [img_log] 生产 硬件工程师 硬件测试工程师 PCB 硬件 工程师 硬件工程师设计出错是什么体验? |

|

怎么又被邀请回答这个问题,就喜欢看人翻车嘛 |

|

|

设计出错是什么体验?当然是内疚后悔...才怪呢,我就设计错怎么了,还能把我开除了不成(叉腰 |

|

|

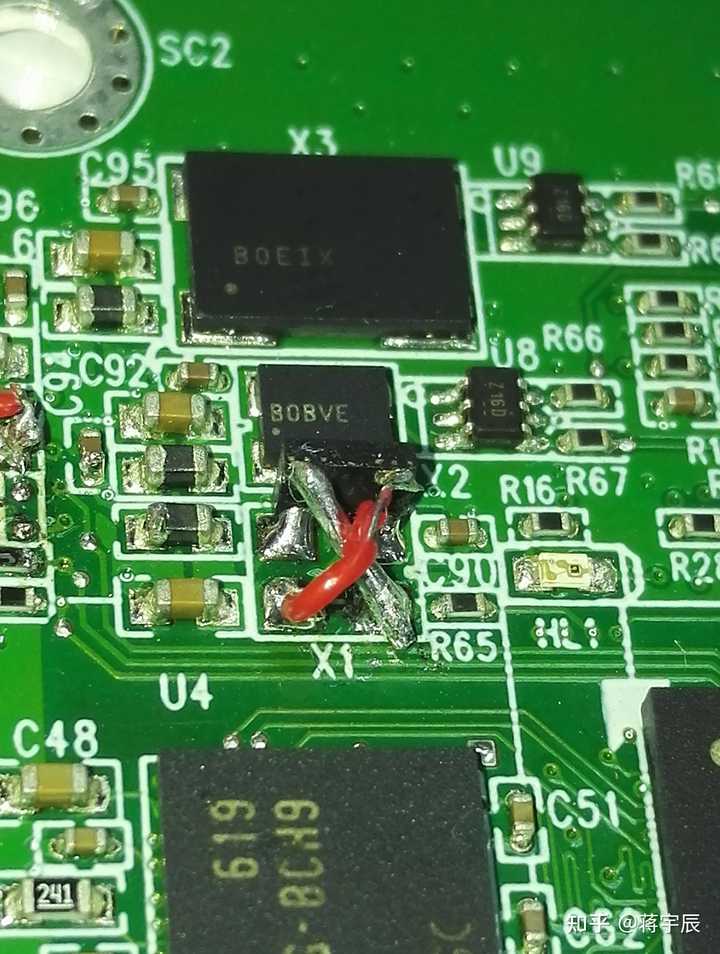

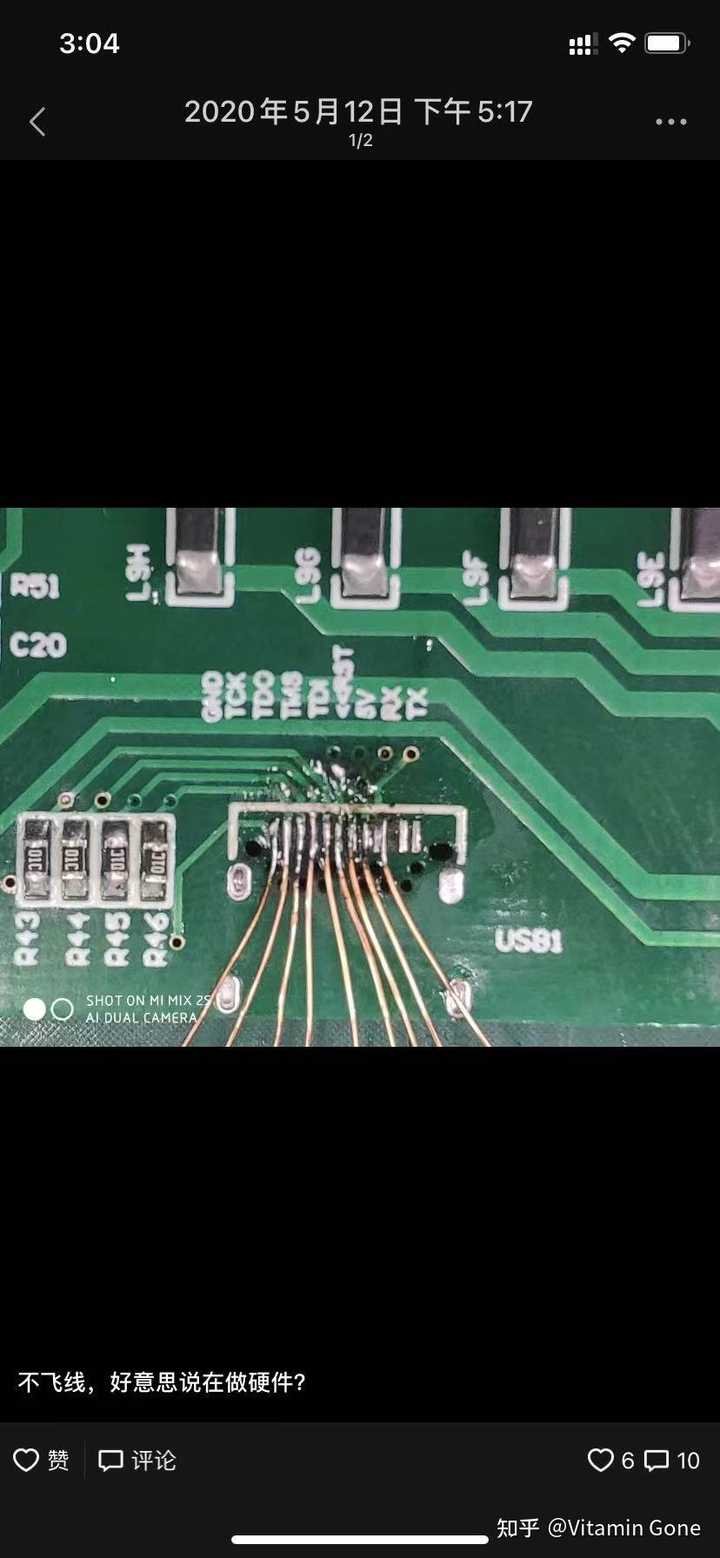

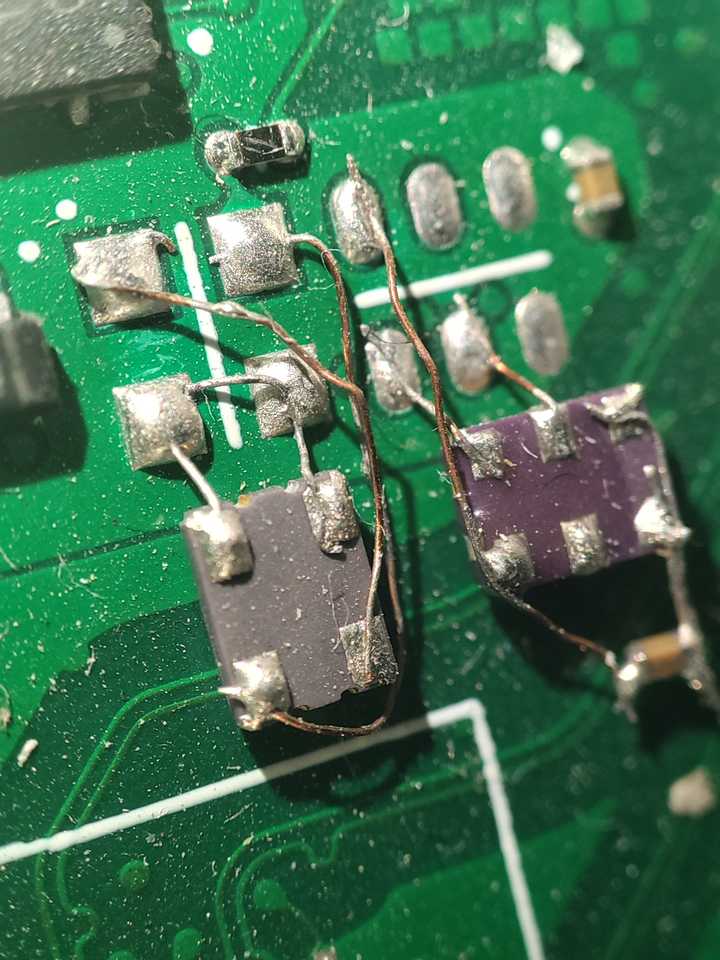

啊不是,老板,不是,我开玩笑呢。是是是我这就去修,保证能用! 晶振两个脚画反了?简单,立起来再交叉飞跟线,完美。 |

|

|

硬件配置字与软件不匹配?改软件去啊。什么,软件忙不过来没人改?!好好好,我改,我改! |

|

|

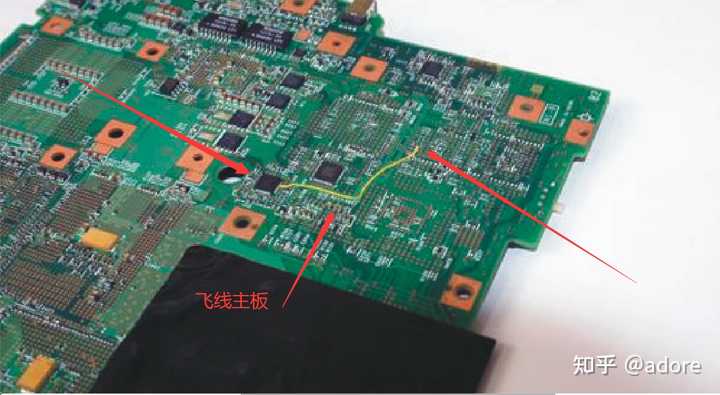

电源俩脚画反了?把脚翘起来飞线完事。(还好没用那种没脚的) |

|

|

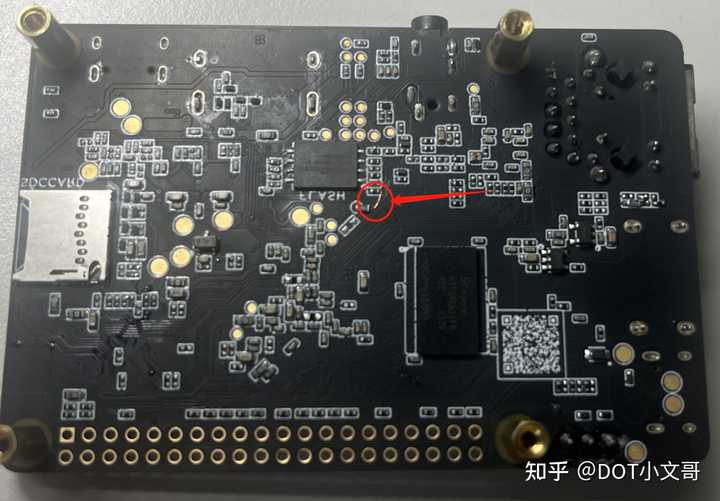

咦怎么不小心把一路时钟驱动器输入接地了???嘿,旁边的兄dei,借个火儿。 |

|

|

软件:你芯片炸了。 我:哪啊,这不是好的么? 软件:你拿放大镜仔细看。 我:......我说了多少遍了不要热拔插不要热拔插不要热拔插!!! |

|

|

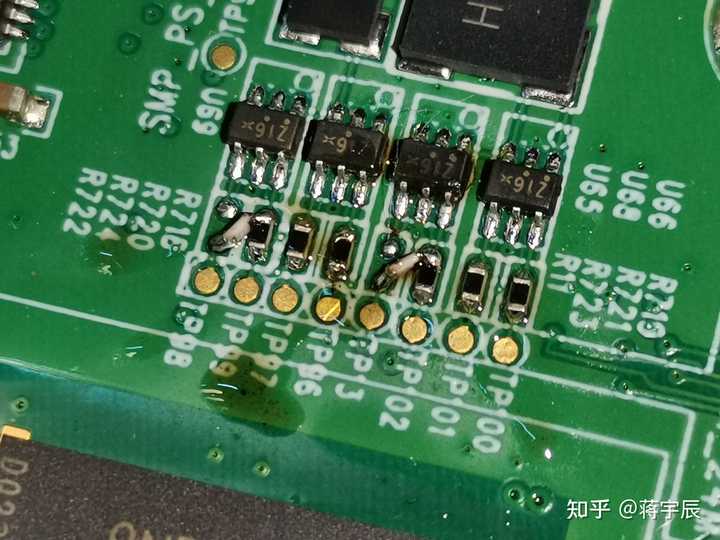

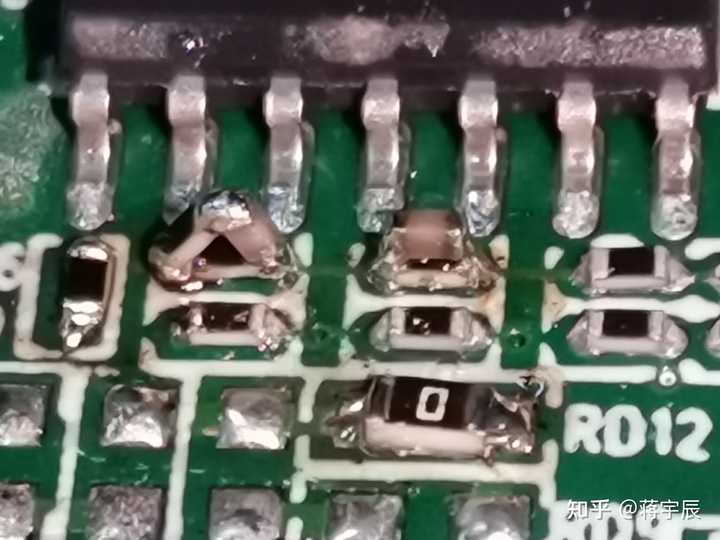

糟糕忘记预留补偿网络的位置了。没关系,SMD搭棚焊接,古典与现代的结合! |

|

|

电容ESR太小导致电压参考环路不稳定,找电源组要个小电阻去。 我:你们有没有小一点的电阻,零点几欧姆那种? 同事:有,给你。 我:这也太大了吧,有小一点的么? 同事:没有,最小就这个了。 我:......算了我想想办法。 |

|

|

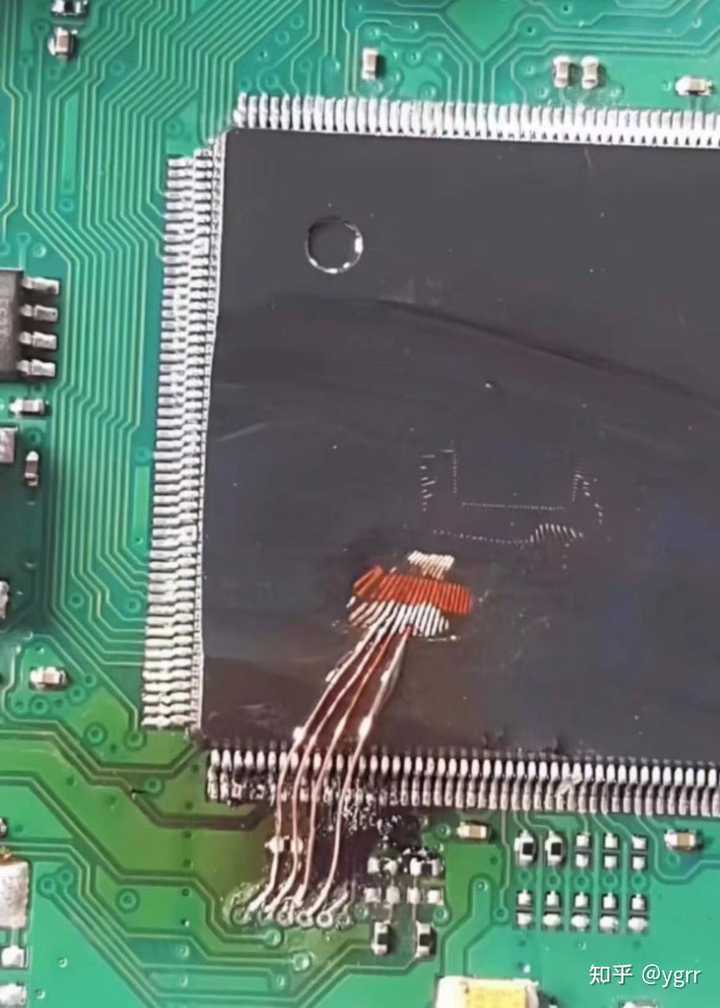

好吧,鉴于总有人怀疑我焊功,我给整个新活,不就是引脚中心间距距0.5mm的QFN嘛,FPC触点抠下来刚好够飞线,看起来就跟原生走线一样。 |

|

|

学会各种骚操作以后就不用怕设计出错了,又不是不能用.jpg 以上纯属虚构,真实情况是这样: 一个单板设计任务下来,前期准备工作、设计工作、检查评审工作所花费的时间接近1:1:1(不是色拉油),我们公司要求原理图设计人逐网络自查(我一般检查2遍以上),项目相关几个同事同行审查,最后还要开一到两次评审会议,通过以后才算完成。 大多数情况下,第一版偶尔有一些不痛不痒的小错误,稍微补救下就完事,不会影响项目进度,下一版改掉就好了。 所以设计出错真没啥体验的,大错误早在设计和评审阶段就给消灭了,偶尔有点小错误也不是致命的。 至于预研项目,项目本身就是拿来试错的,那就是真错得理直气壮。 |

|

软件工程师的问题,反正编译打包成exe以后谁也看不到。 硬件工程师的问题嘛,反正外壳一装。。。。嗨,一拆机看到那些飞线,就暴露了。。。 |

|

啥体验,麻麻的,感觉不对劲,把电拔了,掀开电源板,爬电距离只有2-3毫米,一问,新来的毕业生弄的 补充一下,这个锅不是毕业生该背的,报告给大老板后给新入职的毕业生做了安规设计培训,家电类的3C安规认证依据GB8898或GB4943,这两个强制安规标准是硬件工程师必读必会的。 |

|

当年公司对所有单板硬件设计要求是:“一版成功”(允许BOM的更改,但不能有任何PCB改动,A版本要完成所有的测试(包括入网认证测试)和小批量生产试制,在正式发货前可以小优化一版);所以如果出现任何硬件设计出错,最大的体验是:心如死灰。影响一年的绩效考评啊~ 哈哈~ 为什么会有这么多“连线”错误:Symbol/封装错误,信号电平不匹配,器件选错,芯片启动配置设置错误等等低级错误呢?在我看来是有些不能理解的。 仔细想了一下,我觉得这主要有两方面的原因: 1,对硬件设计工作本身的理解偏差。 2,对于产品质量的压力还不够大:进度压力太大就牺牲下质量吧;第一版单板回来能调通就可以了;大家第一版都会有问题,干嘛这么逼自己……。 这种态度所影响的远不止是表面上所看到的那几个“离奇”问题,而是产品整体质量:硬件设计是一个庞杂的系统工程,我们对这些表层问题都不够认真和细致,那么那些被深入隐藏起来的问题,就更难被排查出来了。 单板硬件的“一版成功”,我认为并非遥不可及:首先自己要建立起这个信念和责任;其次就要有一个系统的硬件开发流程支撑。做到这两点,就远不止是“一版成功”(研发验证测试后不改版)的好处,还能大大提升单板硬件质量。 在我工作的这么多年,经常碰到有朋友认为:硬件设计工作就是“画原理图”和“画PCB”,甚至有筒子们认为画PCB都不算(那属于互连工程师的活)。但我想说的是:画原理图本身只占10%的工作量,1%的技术含量(画原理图只说明你会画图工具而已,“拉线”纯属体力劳动),然而更重要的工作在于前期的分析和后期验证上。如果硬件工程师设计中出现的问题主要是在“画原理图”连线上,那么大概率会有更多、更深层次的问题,远没被发现。等待我们的将是大批量发货后的海量硬件问题(大量的坏板返还维修,头有500斤重,有没有~)。 原理图和PCB中的那些简单设计问题,只需要我们在前期已经做好了知识准备:理解了所有应用器件,掌握了相关硬件知识点(相关总线协议、接口、电源、时钟等);再在执行过程中认真对待,是完全可以避免的。举个栗子:原理图画完后,“板主”应该将每页原理图的器件(特别注意NC管脚)、信号网络(特别注意单网络)检查一遍,如果这次自检有问题就再自检一次,直到自检2遍没有任何问题,再发出来给硬件同事检视;硬件同事一看:哟,都没有简单问题可提了,只好翻器件datasheet、看总线协议,提一些更深层次的问题;所以连线出错、Symbol建错这类问题,不是送给别人检视提的。 |

|

|

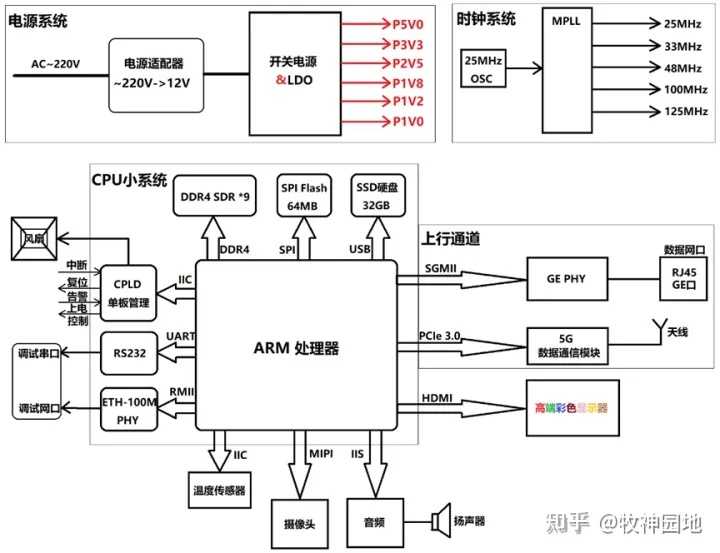

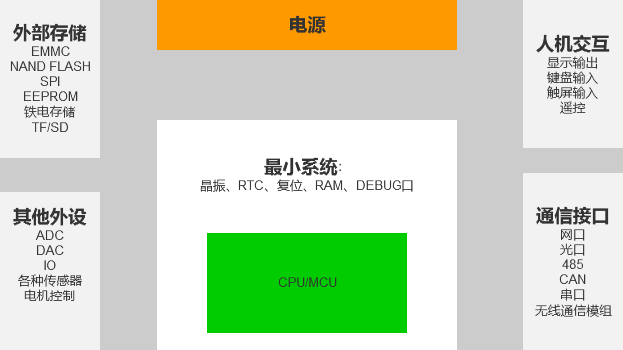

硬件框图(纯属虚构) 接下来我们来看一看作为硬件工程师要怎么来做项目,才能保证硬件设计“一版成功”。需要再次强调的是硬件设计并非只是画原理图和PCB,而是一整个过程;而硬件设计的结果也并非是硬件功能和性能达标,而是硬件单板作为产品的一部分满足产品的实际应用:功能、性能、生产、维护、维修、安装、EMC、安规等等;这是一个工程,而不是在实验室跑一跑的demo板。 来吧,就下来就是干货了: 更多硬件相关知识分享,请关注个人主页“专栏”。 1, 需求分析阶段 1. 需求分解:需求澄清,从上至下需求分解明确、清晰;从下至上需求理解到位,指导硬件框架设计(硬件功能,形态,尺寸,接口,器件等级): 1, 产品需求分解到硬件相关(功能、性能、结构、散热、EMC、安规、环境、认证……)需求; 2, 硬件相关需求分解到硬件设计需求; 3, 硬件设计需求分解到硬件各模块设计需求。 2. 器件资料收集: 详细分析器件功能、性能、接口、是否能满足单板设计需求,分析器件特点以及使用注意事项,为后续单板上应用扫清障碍: 1, 收集单板所使用芯片的最新Datasheet,Application note,原理图参考设计指导等等; 2, 结合器件在单板上的应用情况,分析未使用管脚的处理:JTAG,INT,RST及其它总线等等; 3, 确定管脚内部默认上下拉电阻,确定外部上下拉电阻值选择; 4, 收集器件之前应用涉及案例、使用注意事项等进行学习研究。 3. 专题分析:根据硬件需求划分模块,详细分析、识别各硬件模块相关设计风险,输出书面分析文档,做好硬件兼容设计,设计风险跟踪,指导硬件详细设计和原理图设计: 1, 主要器件选型:根据硬件功能、性能需求,选择适合的主要器件,考虑如下方面:功能,性能,价格,功耗,设计难度,生命周期。 2, 主处理器专题:处理性能,DDR/Flash存储需求,I/O接口形态及数量,功耗/散热,以及软件开发难度是否能满足产品设计需求; 3, 小系统专题:可靠性设计(双BIOS方案、在线升级方案、临终遗言方案,断电保护方案……),硬件解耦设计; 4, 电源专题:电源结构树设计,各电源功耗评估,电源芯片选型,buck电路工作频点选择,各器件电源精度/纹波/噪声需求分析,工作频点计算以及滤波方案设计(主芯片、时钟、DDR……),评估Max(thermal)/Typical/Idle功耗数据; 5, 时钟专题:时钟结构树设计,各芯片时钟需求分析,芯片时钟精度/抖动分析,时钟信号电平分析及匹配设计,简化时钟结构减少OSC等时钟芯片数量; 6, 面板接口专题:面板接口需求分析,连接器排列顺序分析(ID,散热等考虑),告警指示灯位置设计,丝印及条码设计……; 7,总线专题:分析各类总线(IIC,IIS,SPI,PCIe,UART,USB, MIPI, HDMI,)对接电平,不同芯片对接时序分析,总线拓扑分析,总线负载,总线地址分配及支持速率分析; 8, CPLD专题:CPLD需求功能模块分析,I/O bank电平及管脚分配,升级(在线升级及生产加载)功能分析,CPLD内部寄存器分配(测试,版本,告警,控制,上报等); 9, 软硬件接口专题:CPU小系统配置(Flash,DDR),CPU工作模式管脚设置,外设PCIe/IIC/SPI/SMI等接口地址、拓扑,外设芯片寄存器描述。 10, EMC/安规专题:根据EMC/安规标准选取端口防护器件,分析单板高速信号及接口,相关EMC/安规要求落实至PCB和结构设计中; 11, 调测试接口专题:调试UART口,调试网口以及其它调测接口设计, 分析单板上不同芯片的调测通道设计需求(关注新使用芯片),调测试端口初始化阶段; 12, 硬件告警专题:梳理硬件告警种类:在位信息,时钟状态,电源电平,温度范围,风扇转速,芯片异常,软件异常;硬件告警上报路径设计,监测方案设计,上报方案设计,指示灯状态定义; 13, DFx专题: 可靠性设计:备份,冗余设计,减少器件种类及数量,选择失效率低器件; 可维可测性设计:提供更加方便测试的设计(例如:电源/GND标识,测试点,指示灯,异常上报寄存器等),问题定位等硬件支持设计,设计简单可靠BST链路; 可制造性设计:减少插件使用数量,减少软件加载器件数量,选择可焊性高器件,注意PCB布局/布线,尽量简化生产环节/提升生产效率,增加ICT测试点等等。 14, 简洁化/归一化专题:关注分离器件的使用,尽量使用同一编码阻容,同时阻容密集区域可以使用排阻/容进行替代,减少分离器件数量。 15, PCB专题:根据单板功能/散热等要求,对PCB进行预布局,接口连接器排布。 16, 散热设计专题。 17, 硬件调测试需求专题:分析后续调测试及问题定位需求,硬件自身能实现的设计,需要FPGA/CPLD/软件配合的需求(例如:DDR/Flash地址空间读写命令,FPGA/CPLD地址空间读写命令,IIC/SPI/MDIO总线操作命令,告警/中断接口命令, FPGA/CPLD独立升级命令等等),跑满功耗测试软件/脚本/命令等等,详细列出并与相关软件组交流确认。 2, 设计阶段: 1. 硬件详细设计:系统性整合各专题硬件设计,补充专题之间遗漏部分,形成一个有机整体: 1, 整合各专题分析,从硬件整体方面考虑,合成硬件详细设计文档; 2, 统一考虑均衡各专题模块设计,优化设计方案; 3, 补充各专题模块之间遗漏部分,完善硬件设计方案。 2. 原理图设计:清晰的呈现详细设计思想,规范且有条理的实现原理设计;原理图设计过程中思考并反馈完善硬件详细设计: 1, 按原理图设计规范/格式:封页+目录+框图(原理框图/电源框图/时钟框图)+电路设计+更改历史记录; 2, 电路原理图设计顺序,举个栗子:电源+时钟+CPU小系统+周边+调测通道+业务通道; 3, 注意命名规范,统一命名规则,信号名意思清晰明了:电源(例:3V3,2V5),时钟(例:CLK_100MHZ_CPU_PCIE_P/N)等; 4, 统一各模块设计人原理图的格点设置,避免合并时出现错乱异常; 5, 原理图自检,着重检查单网络,避免命名细微差异导致网络不通,确保无简单错误为止; 6, 组织原理图检视,根据问题收敛曲线安排4~7轮左右检视。 3. PCB设计:是硬件工程设计具体实现和呈现,充分调动各不同领域专家对PCB进行检查/审核,保证硬件各指标(功能/性能/热/DFX/可靠性/认证…)满足要求: 1, PCB工程需求文件:硬件工程师提供给PCB工程师工程需求文件,保证一般指标满足需求。 2, PCB预布局,确定PCB各区域模块分布,摆放电源、主芯片、连接器以及风道相关器件,用于热仿真;根据单板最大密度走线区域评估,确定单板的叠层设计; 3, PCB布局设计:根据业务传输总线顺序放置相关主芯片,电源,时钟器件就近使用芯片放置,详细分析/考虑电源、时钟、温度监测点放置,匹配及滤波阻容的放置,注意热敏感器件放置(电解电容、时钟、热敏电阻等),根据布局情况更改原理图设计,注意器件间距设置,结构限高、禁布区域,散热风道设计等; 4, 关注PCB布局可维可测性,例如:两个高大器件中间夹着0402阻容导致不可拆卸;关键电阻(Version,信号串阻,芯片配置电阻等等)尽量放置在Top面便于调测更改,高器件放置距离半边>3cm,避免工厂生产运输过程中撞件;调测用插座/针需要规划齐整并放至裸手不易拿捏处等等; 5, PCB布线设计:重点关注时钟,复位,高密高速总线设计,电源的布线/层设计,关注总线拓扑是否按照计划设计; 6, PCB布局布线检视活动:1,硬件工程师结合原理图设计,关注PCB合理布局/布线;2,推动热设计/结构/工艺工程师进行各自领域合规性审查;3,硬件单板负责人先与PCB工程师进行自检,排查简易问题后再发给大家进行深入检查; 7, 关注PCB布线可维可测性,例如:增加不同电源的丝印表示;信号预留末端过孔或测试点;关键信号预留TestPoint;根据单板布线密度,预留GND孔用于调测使用; 8, 仿真:重要信号:高速,时钟,复位以及长拓扑走线总线信号选择性进行仿真;着重对DDR信号进行仿真,根据仿真结果选择驱动能力及末端匹配设置; 9, 投板:工艺相关风险识别,PCB厂家工程邮件确认,高速信号阻抗控制; 10, 识别并记录风险点(不确定的技术点),便于在单元调测试时增加测试用例进行回归验证。 4. 热设计:保证单板散热设计满足系统需求: 1, 系统设计阶段,要求热设计工程师初步评估不同能力风扇对应系统以及单点最大散热能力,确定多种组合方案; 2, 器件选型时关注主要器件功耗以及散热能力的评估,支持主要芯片选型工作; 3, 做好单个器件功耗以及整板功耗的准确评估,避免出现过设计; 4, 识别风险器件以及区域,PCB布局阶段确定系统散热方案,针对散热风险点确定散热方案(例:特定风道设计,面板开孔位置设计等); 5, 根据热设计仿真结果进行改进和调整,散热效果以实际测试为准,找到热风险点; 6, 记录并跟踪热设计风险及问题,在热测试中进行验证和回归。 5. 结构/工艺设计: 1, 详细设计阶段确定设备具体形态、尺寸、接口,结合热设计,作为结构设计输入条件; 2, 在设计前期(器件选型)与结构/工艺工程师沟通识别风险点,配合PCB设计阶段解决; 3, 配合结构/工艺进行设计PCB排查,避免相关规则被遗漏实施; 4, 结构关注点:(1)单板/Unit螺孔设计要保证结构强度,又不能增加生产复杂度;(2)注意接口的屏蔽设计,开口不能太小安装困难,又不能太大导致EMC问题;(3)导向柱/槽公差设计需匹配连接器,正常安装;(4)结构件配合系统散热,进行风道设计,达到最优;(5)结构设计方便板级插拔,容易操作,框机结构方便搬运/运输; 5, 比对单板结构要素图,确定限高器件、禁布,连接器,接口等位置和开口信息,避免错位; 6, 确定单板加工工艺流程,评估优化; 7, 识别记录设计风险点,待工厂生产安装后进行验证。 6. 功能调测: 1, 专题设计阶段输出“软硬件接口文档”,交付软件/逻辑提前准备相关调测试设计工作; 2, 单板涉及软件(CPLD/FPGA/Boot/主机程序/上电配置程序等)在调测阶段烧写/加载方案,提前与软件交流确认(专题阶段应已设计好),做好相应准备; 3, 提前与软件交流好所需的常用调测工具、命令、脚本、日志信息等等内容; 4, 调测环境准备工作,准备好电源/散热器/调测串口、网线/JTAG工具/其它线缆……; 5, 输出单板调测计划,列出各关键调测节点:电源(上电时序/电平)->时钟->JTAG加载/小系统->外围芯片加载/启动->管理总线->业务总线->业务通道……; 6, 每日通报:日报总结输出问题点以及识别瓶颈,有助于协调资源投入; 7, 问题定位与解决,软硬件协调对出现的异常情况进行定位; 7. 单元测试: 1, PCB投板阶段,根据单板硬件模块制定单元测试计划; 2, 详细明确各测试用例中脚本/命令,测试点位置、测量方法、判断标准; 3, 明确测试所用仪器(示波器/探头)、组网、软件版本信息; 4, 测试GND点采用就近原则,避免由于接地点选择原因引入干扰; 5, 特别关注:(1)电源噪声、纹波及环路参数测试;(2)高速差分信号测试;(3)对外接口信号测试;需要做好分析,提前协调周边部门支持,做好测试仪器准备工作; 6, 做好测试问题记录和跟踪,及时定位解决; 7, 单板测试报告组内会议评审,有不明确的地方需要重新测试。 8. 结构试装: 1, 设备安装难易测试,单板是否可以轻松安装,磕碰板上器件,螺钉数量适中,安装程序要符合习惯思维,避免工厂生产出现异常; 2, 检查设备安装过程中,安装螺孔是否对齐,单板和结构件是否存在干涉情况; 3, 结构件之间安装是否能完全匹配,是否存在松动或间隙过大等问题; 4, 单板对外接口和结构件一致性检查,LED/电口…是否对齐,插拔是否方便; 5, 单板对外接口与结构件之间屏蔽检查:结构件开口与簧片之间接触情况,是否有喷漆等; 6, 面板丝印可读性和美观检查,确定丝印无歧义,整体美观整洁; 7, 检查是否有可能会导致人员身体受伤的电气裸露,孔、棱角、铁片等等; 8, 面板出线规则是否满足应用环境(机架,抱杆…)的要求。 9. 环境/热测试: 1, 设备准备:获取满负荷调测测试软件版本/命令、组网方案、单板及结构件全套,导热硅脂; 2, 测试脚本准备:需覆盖单板所有硬件功能模块,并在出现异常时上报告警; 3, 组网准备:完成所有功能模块以及组网测试验证,常温长时间运行Pass; 4, 温箱环境:选取合适的温箱,根据需求条件(环境温度、风速等)进行测试验证; 5, 测试点准备:根据热仿真选取温度测试点,包括进风口和出风口温度; 6, 结构件组装/安装到位,避免风道出现偏差; 7, 全程记录单板温度传感器及温度计测量数据,监测是否过温以及校验温度传感器偏差; 8, 关注设备运行状况,记录运行log,定时查看是否出现异常告警/重启/功能故障等等,及时定位解决。 10. 摸底/认证测试: 1, 准备软件正式版本、脚本、命令,业务组网设计(可以打通业务通道),日志工具; 2, 准备正式生产单板及结构件(一套),跟发货标准一样; 3, 同EMC工程师一起确定测试标准; 4, 准备测试辅助设备及相关线缆(业务、接地、调测线缆等等); 5, 审查单板各芯片工作时钟及频率频点,审查各接口(调测、业务、电源接口等等)防护是否能满足安规需求; 6, 验证测试组网环境,并长时间跑业务,确定设备运行稳定,无异常log; 7, 认证测试检查:(1)检查设备单板、结构件是否齐全并安装到位; (2)检查接口线缆安装是否OK;(3)检查接地线是否安装到位;(4)供电电源是否良好。 11. 生产试制: 1, 生产试制单板数量确定:统计各组所需单板数量,包括软开发(问题调测,版本发布验证),软硬件测试(功能、性能测试验证),硬件开发(单元测试、问题验证测试),认证测试(安规、EMC…)等等; 2, 新物料采购/样片入库,老物料做提前备货,提前2个月进行物料的排查和备货; 3, 生产测试设备、方案、软件版本以及工具准备等; 4, 跟踪生产装备测试误测,支持相关问题解决; 5, 生产跟线:打通生产流程,各环节跟踪,支持解决各环节存在的问题,优化生产工序,提升生产效率(节省环节,优化测试时间……)。 ~欢迎关注、点赞和收藏,谢谢^_^~ |

|

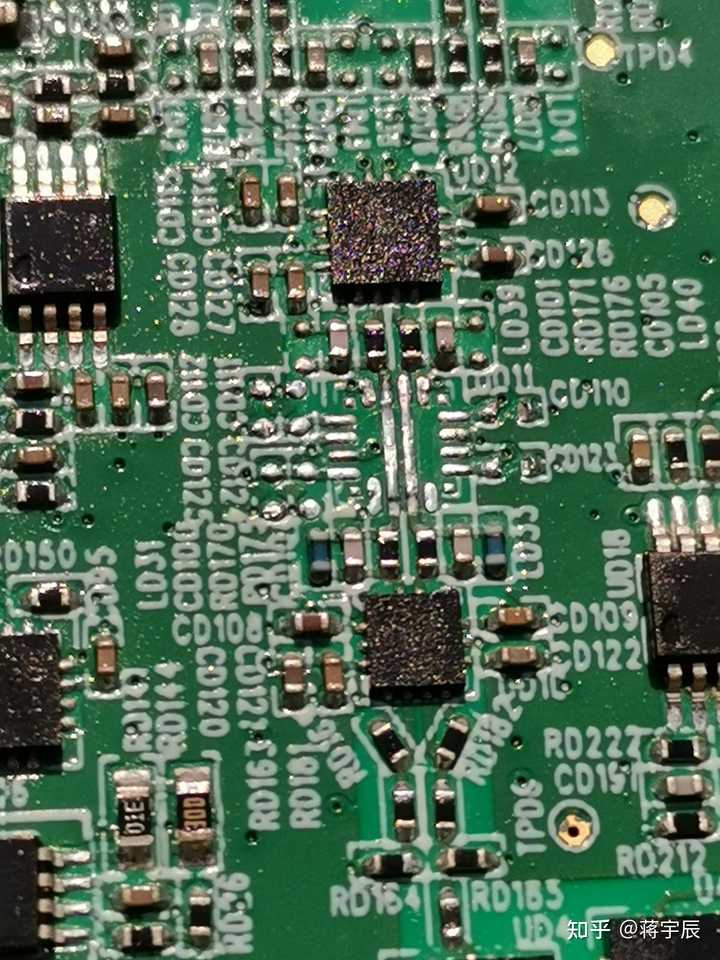

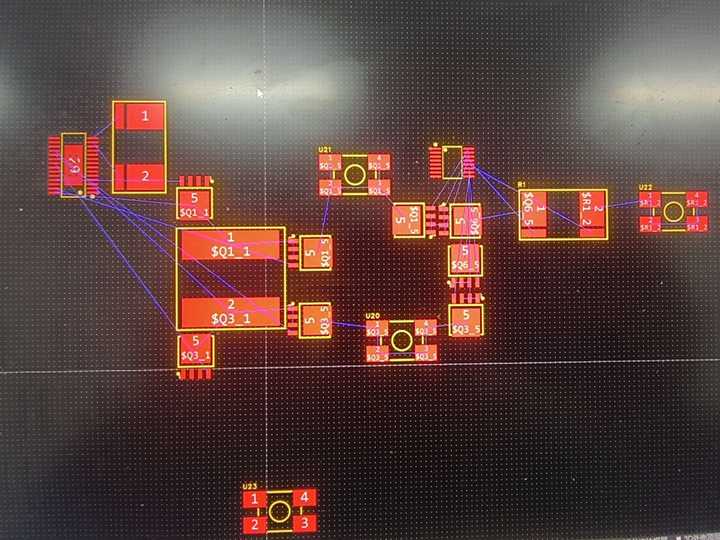

15年到现在,八年了,作为公司硬件团队的负责人,每年十来种8层以上的板子,只去年一块板子做过第二板,剩下近百种板子全部都是一版成。 基本都是这种规模的板子。一旦完善的设计流程形成了,成熟验证的中心库建立起来,硬件设计基本就是一个认真认真再认真的体力活儿了,现在公司招的都是应届本科毕业生,来了半年都能零失误…… 新增: 我是想在这个问题下说如何让硬件工程师失误降低,这些对硬件工程师的成长肯定是不友好的,硬件工程师就是靠炸板子和不停地改版成长起来的。 |

|

|

|

|

|

|

|

错把mm当成mil |

|

|

以前在知乎上看到的,现在画板时候一直特别注意单位 |

|

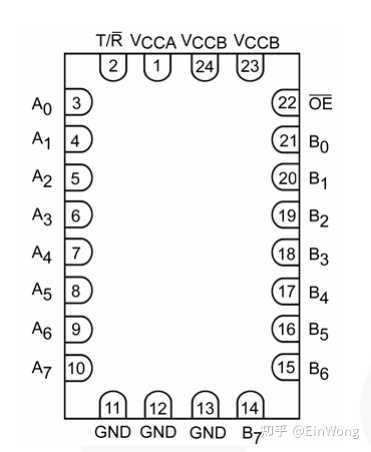

你就看这个pin out图哪里不对劲? |

|

|

正常芯片1pin不都在左上角吗???你把1pin顶脑门上干什么呢??这还是个QFN封装,飞线都没得飞,做出这种封装的厂家可真不是个东西...不说了我去改板子了 |

|

|

|

|

|

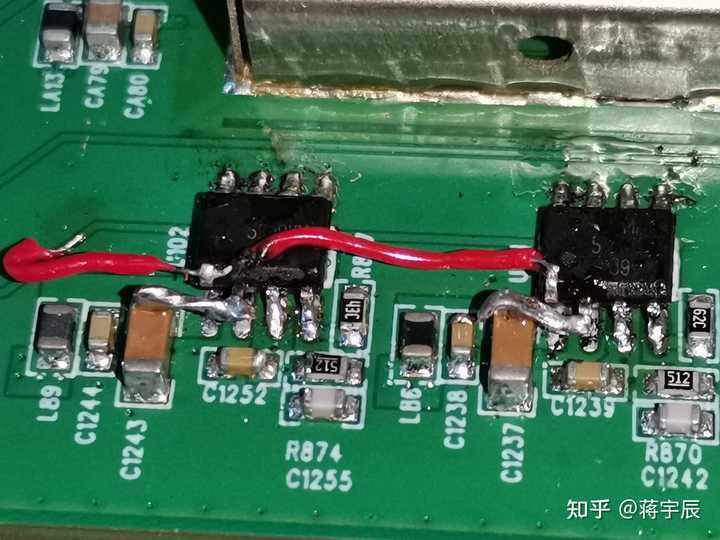

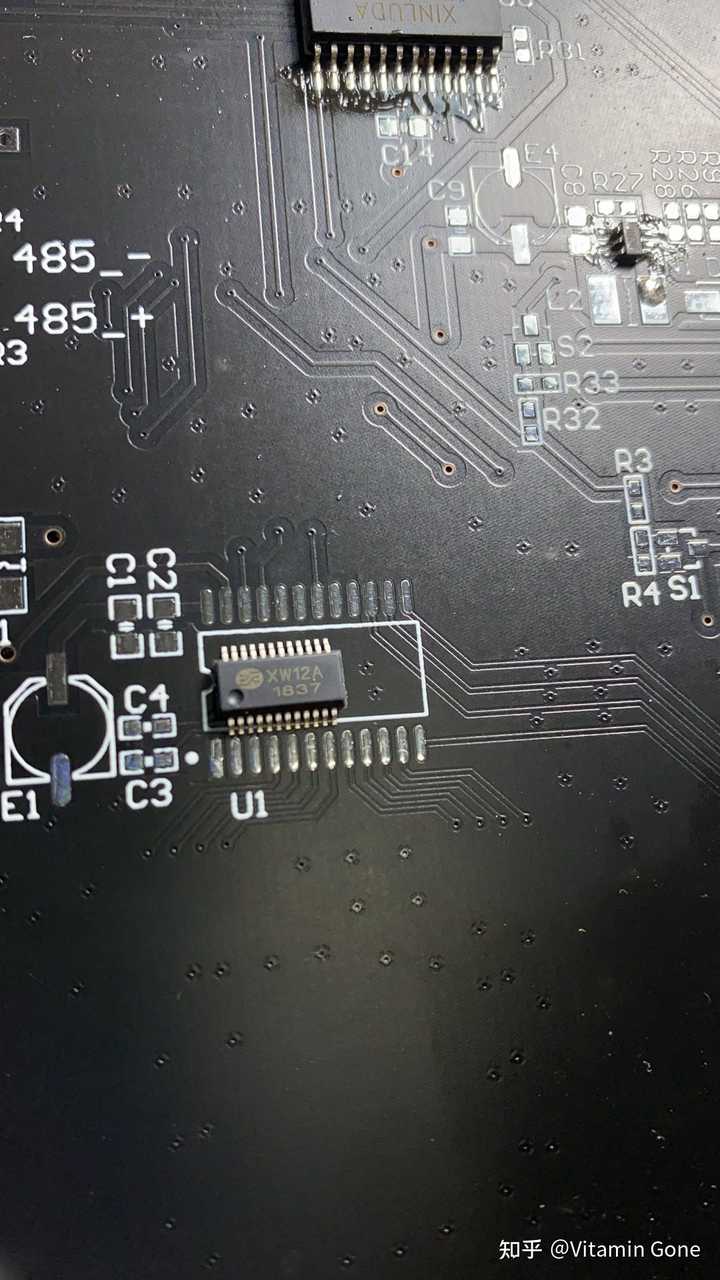

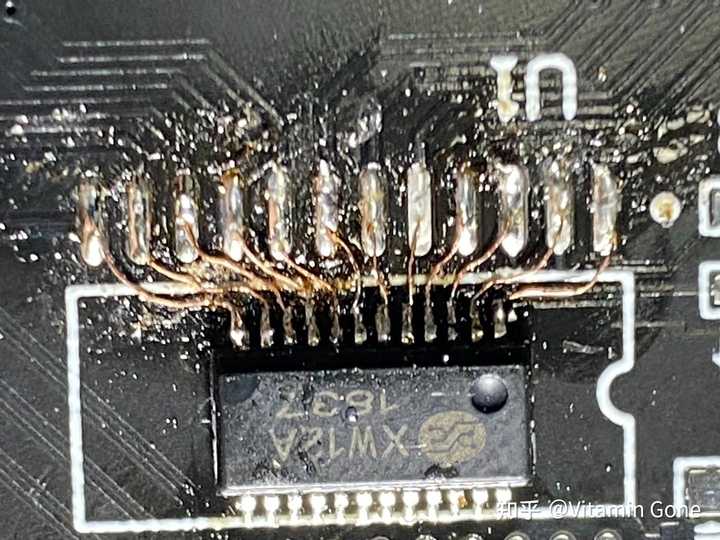

如图,之前某硬件工程师设计的板子,一个设计小错误导致图中这个地方要飞线,就这么小一点,50块板子,飞线飞到眼睛都花了,硬件主管带着小弟在焊接房飞了一个下午。 有一次客户也是,到了小批量试产阶段才发现一个小错误,也是要飞线,2000块板子,因为赶交期,硬件部门连主管几号人+工厂焊接技工在工厂飞了三天三夜。 最大一次见过七八千块板子要飞线的,硬件直接现成辞职了,当月工资都不要了。 ――――――――――――――――――――――――――――――――――――― 评论区有人问“为什么是到了打样生产了才发现?” ―― 你们都是学生没做过项目吗?这不是项目日常吗?有些是概率性问题,要批量测试才能复现;有的是改了一个地方,导致新的问题引入,测试不充分;有的是使用率很低的功能,测试没有覆盖…… 反正各种原因 你想想汽车刹车还有可能测试不充分没发现问题,要等车大规模卖出去之后才发现,然后召回。 飞线能够解决说明设计问题还不算特别大,特别大的板子都废了全部重新打板生产了。 “为什么硬件工程师自己飞线不请个工人飞?” ――这也是一个很学生的问题,你想想那种场景,硬件工程师在产线跟生产,突然发现一个问题是自己设计造成的,那种羞愧感,一般都会带点自责自己就主动走上产线焊接台了。 而且产线的工人也是有自己的工作排班的,不是有钱说请就能请到的,工厂调人也是要协调各方资源的,工程师都是老实人居多,卖面子开口不如卖体力。 ―――――――――――――――――――――――――――――――――― 再说一个,以前魅族的手机专门有飞线版的,就是早期量产的版本,为了不浪费,飞线版也会拿来卖,会直接注明“飞线版”,便宜一两百块钱 |

|

看 到有老哥分享了飞线,我也有点按捺不住。 |

|

|

|

|

|

|

|

|

封装画错,美滋滋。。。 |

|

|

|

|

|

|

|

这个问题很久远了! 大概十年前,X组里一个layout工程师画了几天的pcb,在自觉的没问题的时候提交给了小组长,恰好的是小组长因为开会把未经严格审核的图纸直接批量生产3k,板子来了后,上电,啪嗒一声,嗯呢,冒烟了! 再来一块,接着冒! 还来一块,又冒! 突然意识到,是不是板子问题!!! 3000多块fpga的板子,6层布线,损失多少呢? 罚了小组长3w,再也不敢不看板子了 |

|

刚毕业不久的时候 记得有次 钽电容电容 没标记耐压值。 采购从中关村直接买回来 批量焊接上了。 一共2000片, 上电老化的时候, 比过年还热闹 |

|

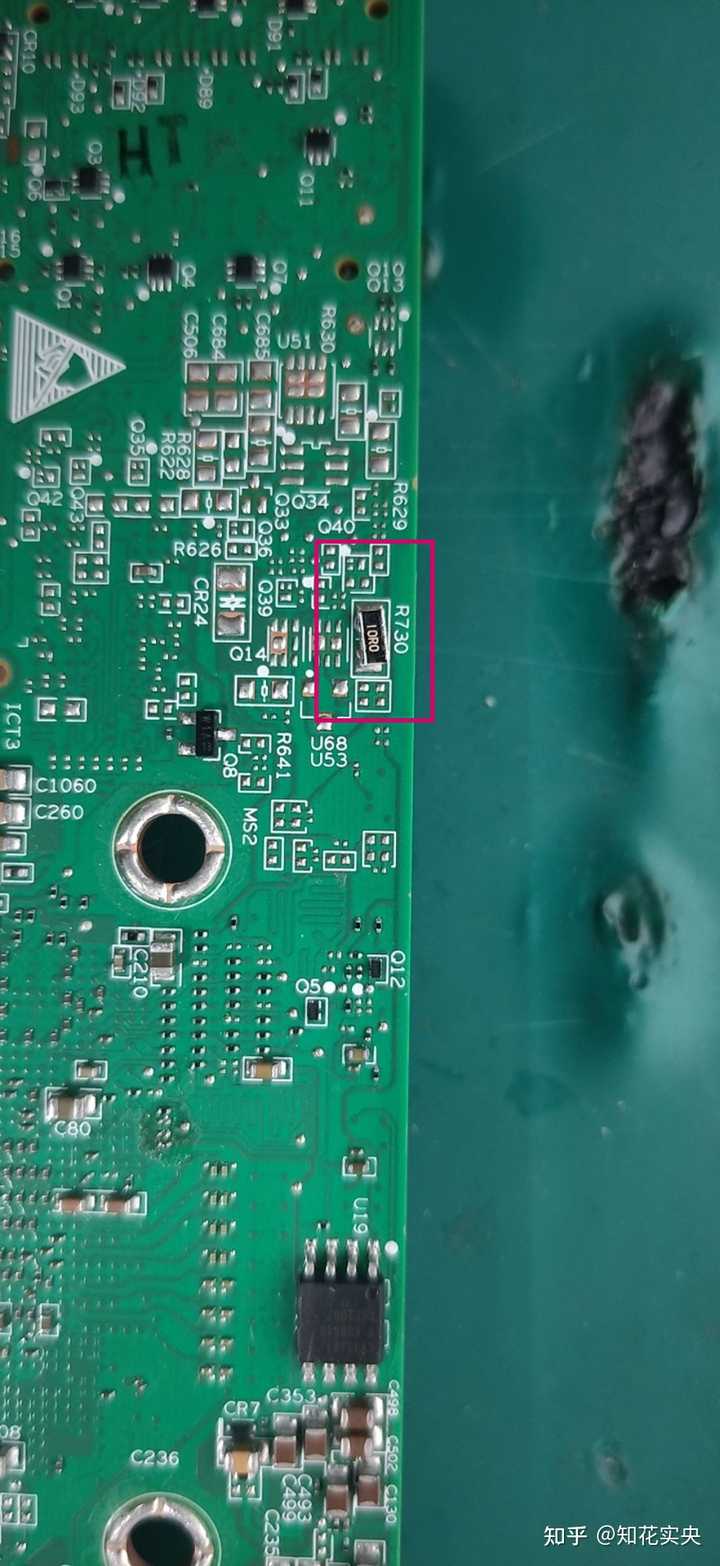

电流监测电路,死活读不出来数据。直到吧这个10欧姆的电阻拆了下来。 |

|

|

|

|

|

这是我在工作上见过最离谱的事。 |

|

我和其他硬件工程师说的最多的一句话:“硬件设计最重要的风险控制”。 大家做产品设计,应该知道,大量的设计都是有参考设计的,通过分析产品或项目的需求,确定主方案以后,就是各种参考设计的应用组合,现在极少有从0开始的设计了。 这里有人一定会说我,你这样的抄来抄去叫硬件设计吗?但事实就是这样,现在芯片的集成度和成熟度太高了,芯片厂家为了快速促成贸易,也会做大量的工作来提高硬件工程师的效率。 其实“抄”也是一种能力。 因为没有那么容易的,任何一个电路模块,你放到自己的方案里,方方面面需要靠的东西太多了。 以数字电路为例,单板设计时我会考虑哪些点:不同关联器件之间接口电路设计,IO电平匹配。单元电路功耗与板载电源总功耗的考量。时序上的设计,逻辑时序和电源时序,有时候电源的上电时序不被人注意,这种故障又比较难排查。一些不起眼的引脚,即使不用,也要一个个检查过,了解他们的作用,很多引脚和芯片的工作模式息息相关,一些上下拉要预留。LAYOUT时高速信号、敏感器件和信号的处理。每个器件的引脚封装设计要细细检查,特别是自己画的封装。BGA等封装的电路设计,不能有任何闪失,跑不起来就是废板,费工费时费钱,项目也拖不起,会很难堪的。考虑冗余设计,为自己认为不可控的因素留出补救的余地,至少第一版有点小问题飞飞线是可以接受的。 先零散的写这些,其实真正项目中会遇到方方面面的问题。 有时候项目紧的时候更加要理清思路,学会拒绝,我和老板说过,你希望我2个月做1版,还是3个月做2版? 想做硬件工程师,有什么推荐的书吗?472 赞同 ・ 26 评论回答 |

|

|

森山:如何打造自己的低成本电子实验室?2043 赞同 ・ 261 评论文章 |

|

|

硬件工程师如何零基础入门?508 赞同 ・ 137 评论回答 |

|

|

森山:一条布的诞生-DIY纺织机控制系统164 赞同 ・ 23 评论文章 |

|

|

如何系统的学习单片机?560 赞同 ・ 25 评论回答 |

|

|

送给大家一份自己写的Cadence自学教程,也许用得着: 森山:60天掌握CADENCE-电路设计原创教程1130 赞同 ・ 129 评论文章 |

|

|

|

|

给仪表客户设计一款NFC读卡模块,样品焊接人员将560nH电感错误焊接成了同样封装的270nH,我在这个情况下调完匹配参数给客户送样演示,客户表示很满意,遂批量生产。第一批3000片,全部无法读卡。?????? |

|

让我知道几百兆的飞线似乎没什么问题 |

|

|

|

|

改呗,还能咋滴。试制出错再正常不过了,大厂也一样。 |

|

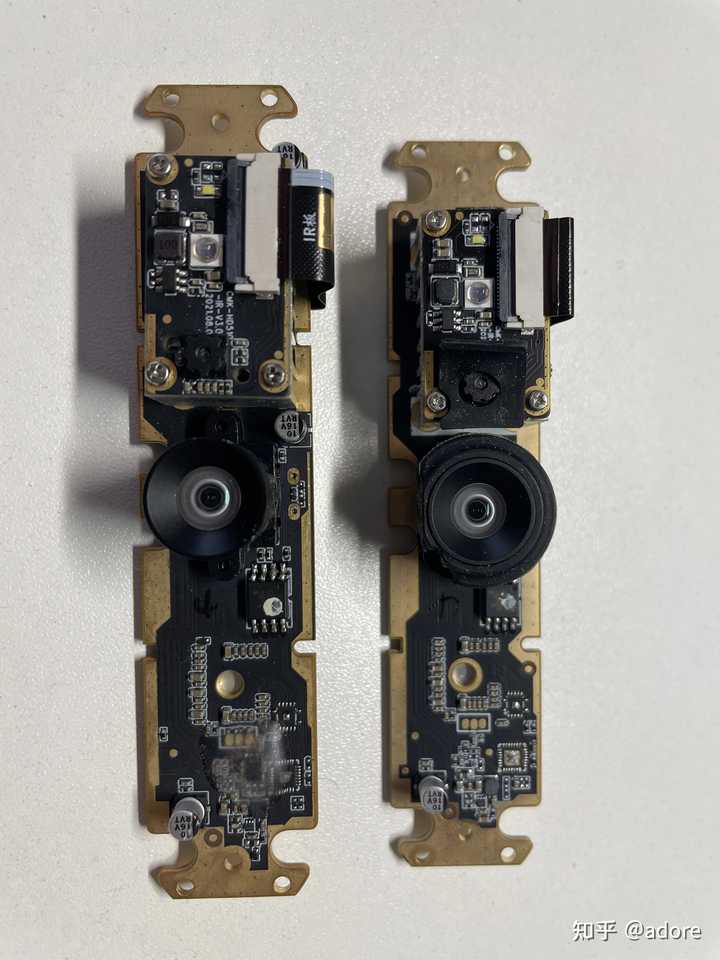

|

曾经收的俩工程样品,联想的摄像头,左边这不照样是手工飞线,只不过飞的规矩一点还打胶固定,比我上学电子课那灵魂走线漂亮多了。 只不过像当年联想飞线门那样在量产机上搞飞线,那可就丢人丢大发啦( ̄? ̄) |

|

|

|

|

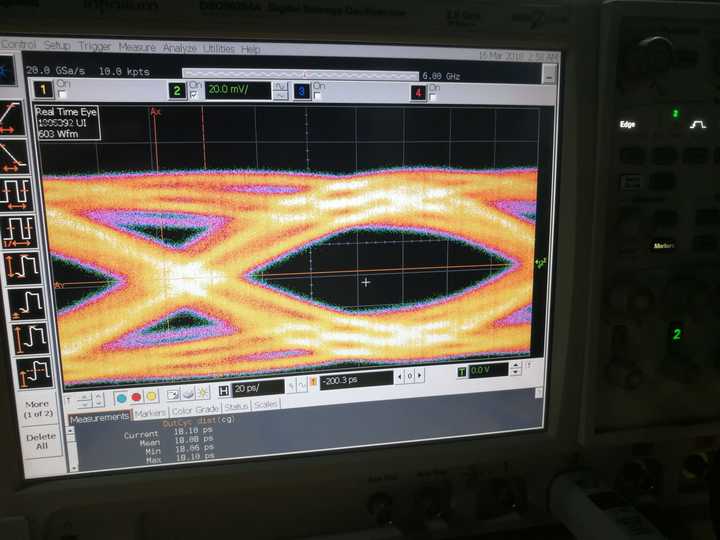

大一时,用ad画了一块单片机的板子,没有出现意外,果然挂掉。晶振封装错了,布局太丑了,让我自己都看不下去。还好是自己画着玩。 大学后期在公司实习,陆陆续续画了10多块pcb,都是双面的数字信号板,基本没有错误。 读了研究生,有机会接触一些高端设计。说说最近的一个设计,板子成本大概是8w的物料成本,有一颗V7的FPGA,一颗DSP,2颗12路10G速率的光模块。 老大要求板子速率跑到6.25G,想想整个系统要跑到这个速度,板子回来前很紧张。 前前后后,原理图到pcb,pcb是16层,做了两个月,制板焊接1个月,一星期前回来,目前板子上电,程序下载都正常。等背板回来测试结果。 出错最可怕的耽搁进度。附一张上个项目的眼图,保佑我这个板子的眼图一样漂亮。 |

|

|

|

|

50块的板子:小事,重打吧,这点钱算啥啊,这个留作纪念吧。 200块的板子:出了点小问题,一切都在控制当中,重新做一套就没问题了。 1000块的板子:这一块设计有问题,我观察电源和高频那块也没考虑好,估计这块板子跑起来会出问题,建议重新做一套吧。 8000块的板子:没办法、没办法,这么多规则怎能不出错吗,重新搞,不就是一个月工资嘛。 10000+的板子:(把脸拾掇拾掇)那啥,这次设计出错责任主要在我,我辜负了公司领导的信任,对不起党、国家、人民对我的培养,在此郑重道歉并写下一万字总结,在在下一次的设计中保证不会范同样错误。 内心:千万不要调错板子,千万不要飞线,千万不要割铜皮,会死人的。 废弃的板子:哭晕在抽屉。 (前几个个人体会,后面的想象加胡说八道) |

|

tcp死活通信不上,查了时序和手册后发现phy芯片一个电阻接错了,导致有2ns延时…… |

|

16年底公司接了一个返修的订单,巴掌大的pcb上BOM搞错了十来颗0201的电阻容,总共几千块板子,后来听说这家公司的硬件部门的员工全部炒掉了。 |

|

打RoboMaster,全队硬件就我一个,真・抗压王。 24年底更新:硬件组组长+副队长,所有机械和电路的项目都是我辅助项目管理负责。 先做超电,一个月迭代了4个版本。 然后飞镖的两个接口画反了,我当时疯狂飞线……赶在比赛之前弄完了。 还有各种杂项的维修,整个突出一个寄。 好了,终于要招新了……还要写大纲,习惯了,什么是LaTeX糕手啊(战术后仰) |

|

|

|

|

|

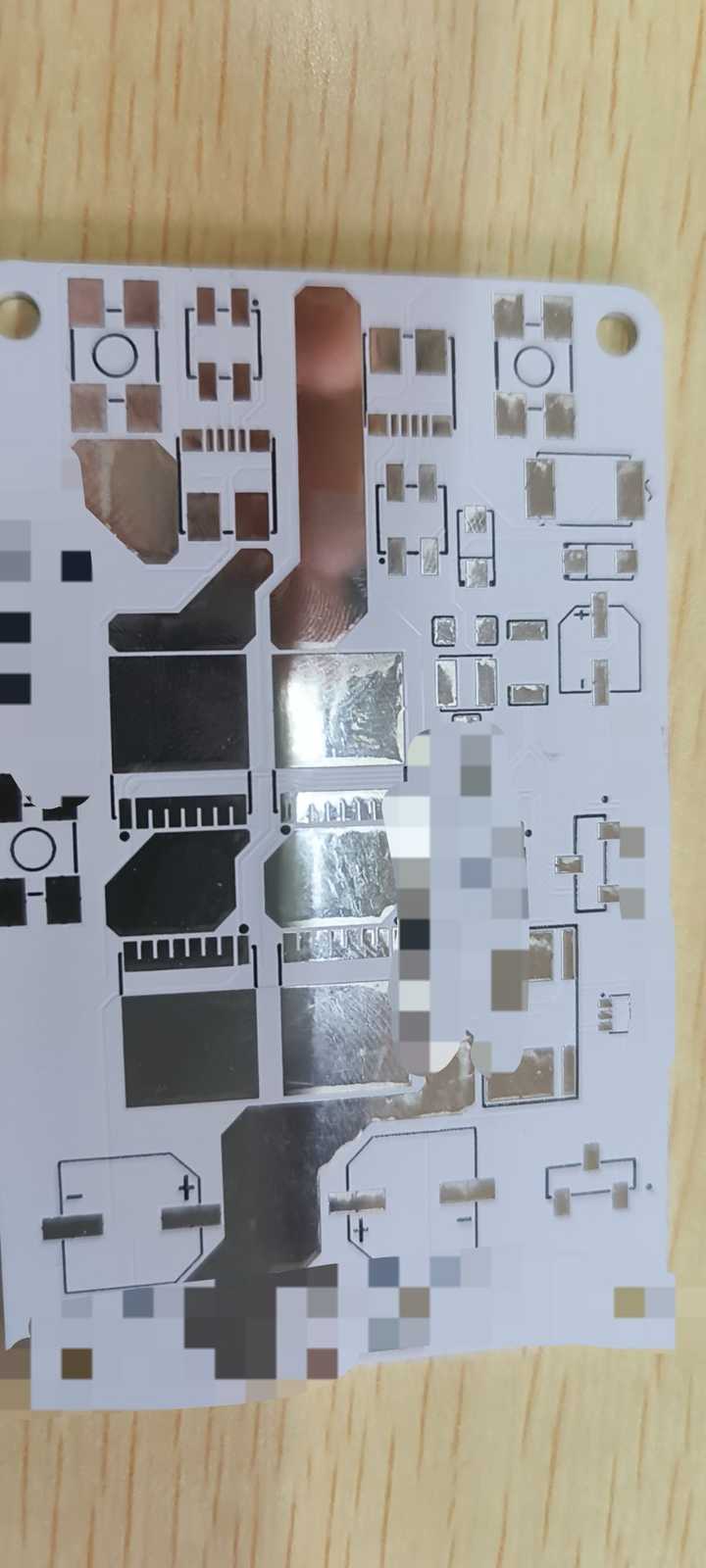

二代超电设计图 |

|

|

超电功率板 大一打智能车,一个过孔把电源和地短路了,我最后直接钻孔解决,事后检查,是我多按了一次鼠标…… |

|

|

[此刻这两块板子还不知道自己的厄运] |

|

我还是学生,说说我的经历吧。17年电赛F题水情检测,东西什么都好,测量也准确,评委说如果后面也没问题可以送国赛。后来测pH值加醋加多了pH太低评委说把水倒了重新加醋,因为我们考虑不周、配合不好,板子没固定,倒水的时候板子直接通电状态下掉水里,水里还有醋,卒。 后来给评委说了,评委嘴张的比我们还大,然后,没然后了。。。 |

|

1.之前一款PCBA出过很多货,都没问题,后来有个客户要用到电机上,几千片,出去出问题,异常保护,回来测试发现电机干扰了电流采样,触发过流保护了,然后几千片,全部返厂手工焊接一个插件瓷片电容,直接飞件,因为没有焊盘。 2.还有一款产品,贴片电容出问题,哎,太难受了 ,损失几十万!假电容,产品在北方户外,冬天一过,大批量出问题!这种事情跟供应商扯皮也不好扯,真TM想把供应商揍一顿! |

|

业余玩家,这个算吗? 还有什么串口画反的,太正常了 |

|

|

|

|

|

| [收藏本文] 【下载本文】 |

| 上一篇文章 下一篇文章 查看所有文章 |

|

|

|

|

古典名著

名著精选

外国名著

儿童童话

武侠小说

名人传记

学习励志

诗词散文

经典故事

其它杂谈

小说文学 恐怖推理 感情生活 瓶邪 原创小说 小说 故事 鬼故事 微小说 文学 耽美 师生 内向 成功 潇湘溪苑 旧巷笙歌 花千骨 剑来 万相之王 深空彼岸 浅浅寂寞 yy小说吧 穿越小说 校园小说 武侠小说 言情小说 玄幻小说 经典语录 三国演义 西游记 红楼梦 水浒传 古诗 易经 后宫 鼠猫 美文 坏蛋 对联 读后感 文字吧 武动乾坤 遮天 凡人修仙传 吞噬星空 盗墓笔记 斗破苍穹 绝世唐门 龙王传说 诛仙 庶女有毒 哈利波特 雪中悍刀行 知否知否应是绿肥红瘦 极品家丁 龙族 玄界之门 莽荒纪 全职高手 心理罪 校花的贴身高手 美人为馅 三体 我欲封天 少年王 旧巷笙歌 花千骨 剑来 万相之王 深空彼岸 天阿降临 重生唐三 最强狂兵 邻家天使大人把我变成废人这事 顶级弃少 大奉打更人 剑道第一仙 一剑独尊 剑仙在此 渡劫之王 第九特区 不败战神 星门 圣墟 |

|

|

| 网站联系: qq:121756557 email:121756557@qq.com |